新品發(fā)布 | EsseLint:從源頭攔截設(shè)計漏洞的語法檢查引擎

隨著數(shù)字設(shè)計領(lǐng)域迅速發(fā)展,Verilog/VHDL等硬件描述語言(HDL)已成為電子電路設(shè)計驗證的關(guān)鍵載體。設(shè)計師與驗證工程師面臨日益復(fù)雜的設(shè)計挑戰(zhàn):亟需在早期階段發(fā)現(xiàn)語法錯誤、潛在設(shè)計問題及代碼規(guī)范違規(guī)。設(shè)計團隊因編碼標準差異,迫切要求工具可按項目靈活配置檢查策略。隨著行業(yè)規(guī)模擴張,市場對高效國產(chǎn)HDL Lint工具的需求持續(xù)攀升。

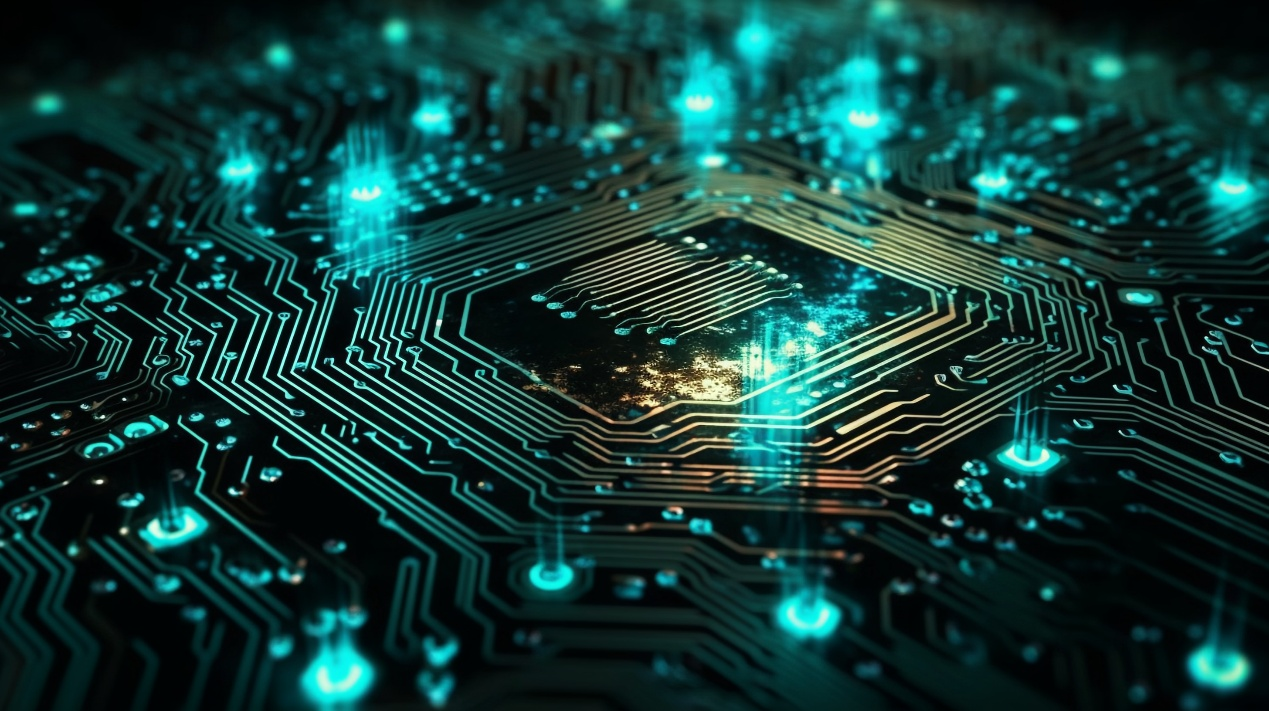

國微芯正式推出芯天成?形式驗證平臺設(shè)計規(guī)則檢查工具——EsseLint,精準響應(yīng)行業(yè)訴求。該產(chǎn)品通過深度掃描代碼風格、語法規(guī)范、可綜合性及電路結(jié)構(gòu)問題,系統(tǒng)性規(guī)避因設(shè)計風格不一致、不合理電路結(jié)構(gòu)和仿真綜合差異引發(fā)的潛在風險,顯著提升代碼質(zhì)量與可維護性,為芯片設(shè)計功能正確性和穩(wěn)定性構(gòu)筑強支撐基座。

痛點鎖定:百萬門級設(shè)計質(zhì)量管控三重失效風險

芯片復(fù)雜度激增令Verilog/VHDL設(shè)計深陷質(zhì)量困局:

規(guī)模激增引爆設(shè)計風險:百萬門級復(fù)雜度下,語法錯誤、編碼規(guī)范混亂及不可綜合代碼頻發(fā),顯著增加綜合流程中斷風險與后期調(diào)試成本。

質(zhì)量隱患直傳導(dǎo)流片風險:仿真與綜合結(jié)果不匹配、電路結(jié)構(gòu)缺陷等隱患因檢測缺失,直接推升流片失敗概率。

傳統(tǒng)工具國產(chǎn)化適配不足:現(xiàn)有方案對140萬Cell設(shè)計檢測耗時數(shù)分鐘級,且規(guī)則僵化難滿足本土定制需求,制約迭代效率。

——效率瓶頸、靈活性缺失與國產(chǎn)化適配不足,構(gòu)成當前質(zhì)量管控的核心短板之一。

破局之道:四大功能引擎重構(gòu)質(zhì)量防線

技術(shù)研新——全棧式規(guī)則驗證引擎

1. 智能規(guī)則矩陣

? 當前構(gòu)建數(shù)百加原子級規(guī)則庫,完整涵蓋:

語法檢查層:實時解析Verilog/SV/VHDL語法樹,精準攔截端口未連接、信號多重定義等基礎(chǔ)錯誤;

規(guī)范檢查層:強制統(tǒng)一命名規(guī)范(如模塊名前綴_信號駝峰法)與代碼風格,消除團隊協(xié)作歧義;

電路結(jié)構(gòu)層:深度檢測組合邏輯環(huán)、鎖存器隱式推斷、時序路徑?jīng)_突等硬件風險,預(yù)防硅前設(shè)計返工。

? 支持動態(tài)規(guī)則擴展,用戶可注入定制規(guī)則(如CPU特有復(fù)位策略檢查),國產(chǎn)化規(guī)則可定制化適配。

2. 超高效驗證架構(gòu)

? 百倍級加速:實測案例中140萬Cell設(shè)計掃描僅需129秒,較傳統(tǒng)工具效率顯著提升;

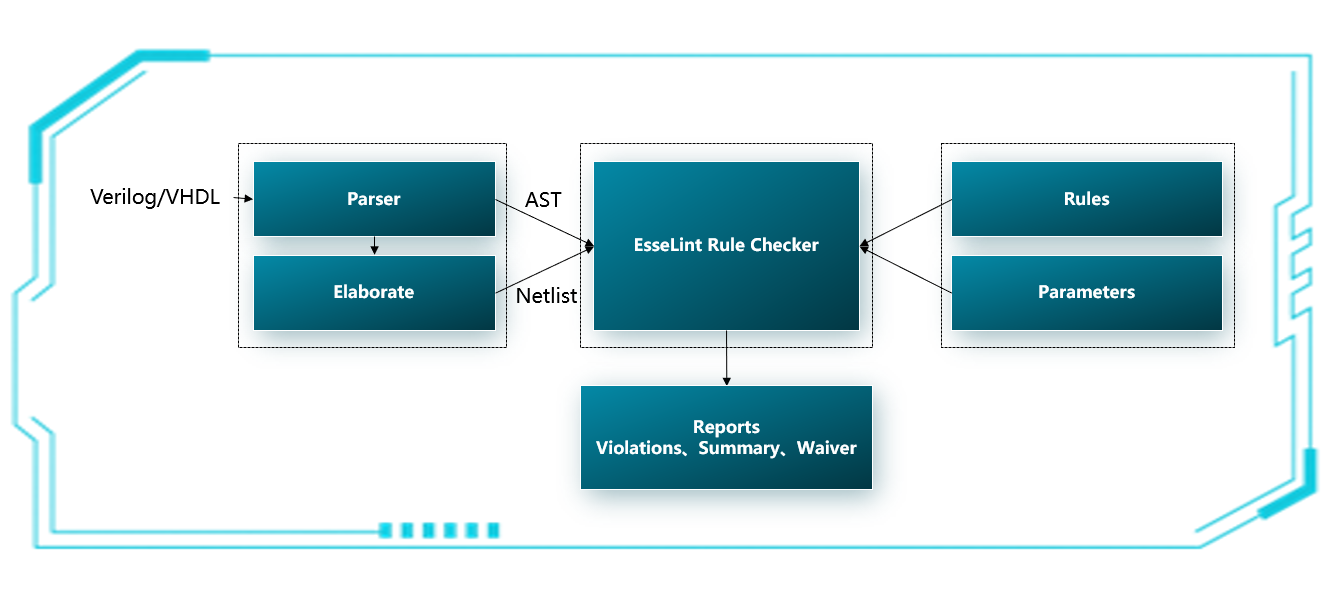

3. 深度診斷報告系統(tǒng)

? 生成四級錯誤追蹤鏈路:

違例類型——錯誤代碼行——修復(fù)建議——waive違例信息

? waive違例信息,支持違例信息豁免,避免重復(fù)確認報錯信息;

? 集成可視化調(diào)試沙盒,支持錯誤代碼段實時修改驗證,問題定位效率精準提升。

4. 標準化流程集成

? 預(yù)置十數(shù)條自動化TCL命令集

主要操作鏈:read_design -> select_goal -> rule_check -> report_gen

應(yīng)用場景:全流程風險攔截體系

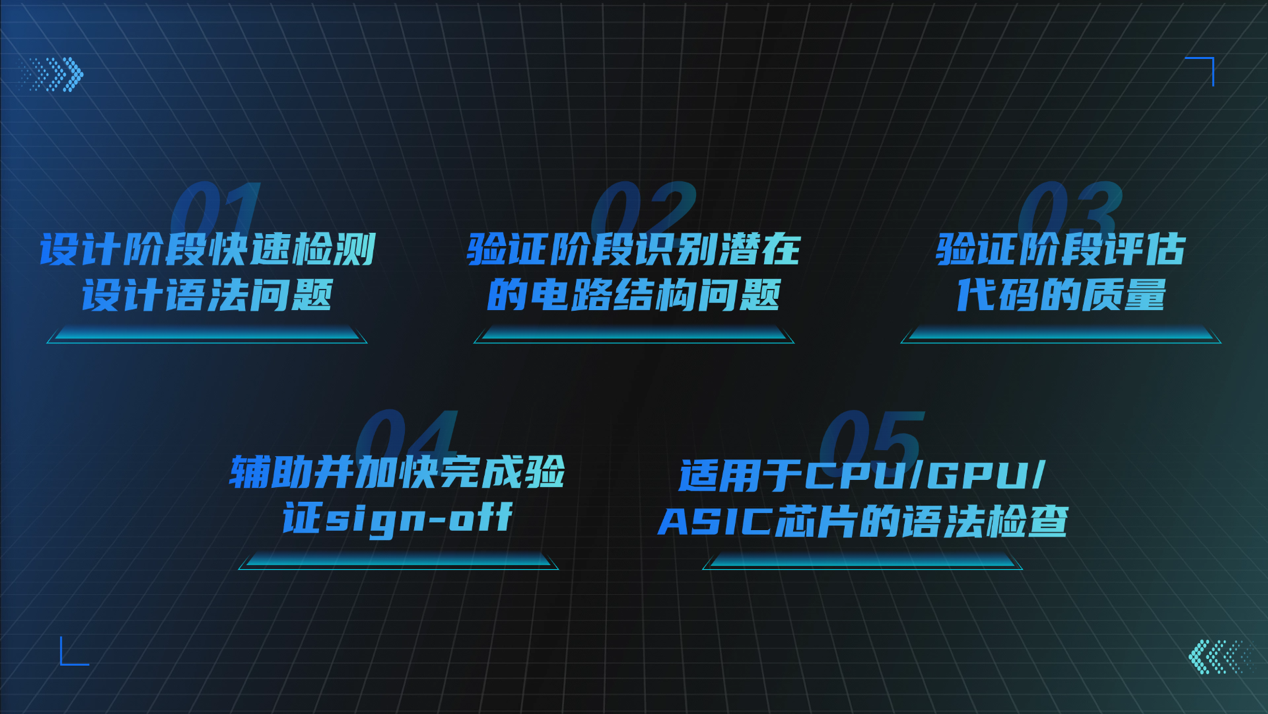

1. 設(shè)計階段快速檢測設(shè)計語法問題

通過實時語法檢查攔截未聲明變量等基礎(chǔ)錯誤,預(yù)防綜合流程崩潰。

2. 驗證階段識別潛在的電路結(jié)構(gòu)問題

深度掃描多驅(qū)動沖突、鎖存器推斷等電路缺陷,消除仿真綜合斷層風險。

3. 驗證階段評估代碼的質(zhì)量

輸出量化評分報告,驅(qū)動可讀性與可維護性優(yōu)化。

4. 輔助并加快完成驗證sign-off

TCL自動化流程壓縮50%簽收周期。

5. 適用于CPU/GPU/ASIC芯片的語法檢查

預(yù)置芯片專用規(guī)則包,全面支持國產(chǎn)CPU/GPU開發(fā)全流程語法護航。支持國產(chǎn)架構(gòu)擴展。

生態(tài)賦能:共建國產(chǎn)EDA可持續(xù)發(fā)展體系

1. 標準筑基:開源協(xié)議與IEEE標準深度互

語法標準對齊:支持IEEE 1800(SystemVerilog)/ 1076(VHDL)語法標準,實現(xiàn)國際驗證流程無縫遷移;

預(yù)制模板:預(yù)置國產(chǎn)CPU/GPU/ASIC等芯片設(shè)計規(guī)范檢查模板,降低本土企業(yè)技術(shù)遷移門檻。

2. 產(chǎn)業(yè)協(xié)同:國產(chǎn)芯片全棧適配生

架構(gòu)支持:深度適配主流國產(chǎn)CPU架構(gòu)設(shè)計規(guī)范,預(yù)置存儲芯片時序檢查等專用規(guī)則包;

工具鏈集成:補齊國微芯形式驗證平臺EsseFormal,貫穿于數(shù)字IC設(shè)計的各個階段,綜合工具共建驗證閉環(huán),為芯片設(shè)計過程中的每個環(huán)節(jié)提供驗證解決方案,兼具定制化和集成化兩大優(yōu)勢,能夠精準滿足客戶需求。

協(xié)同謀新:突破傳統(tǒng)工具效率與國產(chǎn)化瓶頸

國微芯營銷中心總經(jīng)理鄧金斌:“通過構(gòu)建自主知識產(chǎn)權(quán)的核心技術(shù)體系,國微芯為國產(chǎn)芯片提供了高可靠性代碼質(zhì)量保障基座,并推動形式驗證、綜合優(yōu)化等技術(shù)的協(xié)同發(fā)展。EsseLint將有效賦能本土芯片企業(yè),強化國產(chǎn)EDA產(chǎn)業(yè)鏈韌性。未來國微芯將持續(xù)深化形式驗證等核心技術(shù),協(xié)同推動綜合優(yōu)化等方向創(chuàng)新。在生態(tài)上,聯(lián)合產(chǎn)業(yè)鏈伙伴共建開放共贏的EDA工具鏈,助力中國芯片產(chǎn)業(yè)實現(xiàn)全面自主化!”

正和微芯-芯片設(shè)計總監(jiān) 張慶:“EsseLint在超大規(guī)模芯片設(shè)計中展現(xiàn)出變革性價值。其深度規(guī)則引擎顯著提升代碼規(guī)范性,極大解決團隊協(xié)作中的風格碎片化問題;高速解析能力將設(shè)計隱患識別效率提升至行業(yè)新高度,幫助我們系統(tǒng)性規(guī)避流片風險。工具創(chuàng)新的TCL自動化流程已成為設(shè)計驗證不可或缺的質(zhì)量基座。”

EsseLint以智能規(guī)則矩陣、超高效驗證架構(gòu)、深度診斷報告和標準化流程四大功能,精準攔截語法錯誤與電路結(jié)構(gòu)隱患,更以百倍級加速突破傳統(tǒng)效率瓶頸,為芯片筑牢代碼質(zhì)量基座。其深度國產(chǎn)化適配能力,支持動態(tài)規(guī)則擴展與自動化流程集成,顯著壓縮驗證簽收周期。隨著生態(tài)協(xié)同深化,EsseLint將持續(xù)賦能設(shè)計源頭風險攔截,驅(qū)動國產(chǎn)EDA工具鏈自主創(chuàng)新,助力中國芯片產(chǎn)業(yè)構(gòu)建"設(shè)計即正確"的高質(zhì)量研發(fā)范式。